Induction: July 2015

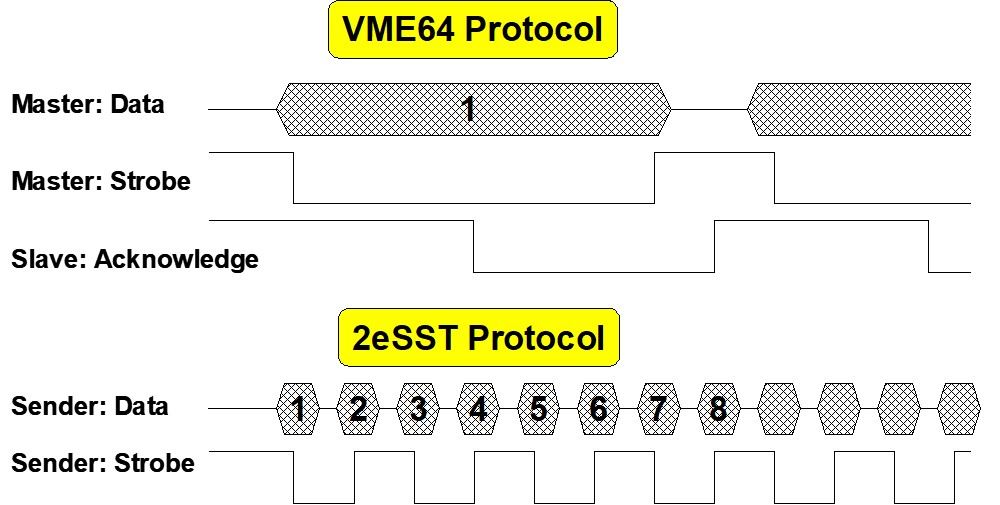

ANSI/VITA 1.5-2003 (R2009) (2eSST) is an extension of the ANSI/VITA 1-1994, VME64, and ANSI/VITA 1.1-1997, VME64x standards. It defines a transfer protocol based upon source-synchronous concepts that permits the VMEbus to operate at rates to at least 320 MBps. As technology improves, this rate can be extended to higher levels. The 2eSST specification emerged out of the MBLT and 2eVME concepts that extended the performance of VMEbus data transfers. Figure 2 compares the VME64 and 2eSST standards.

Thales Computers designed the Alma2e bridge supporting the 2eSST protocol in 2002. Tundra Semiconductor, working with Motorola, brought the Tsi148 PCI/X-to-VME2eSST bridge to market in 2004, making the 2eSST protocol available to the entire industry. Concepts exist to enhance VME2eSST that could increase performance to more than 1 GBps.

The 2eSST protocol requires low skew between signals and monotonic rising and falling edges on the signals. To meet these requirements, limited length backplanes, special backplane topologies, and/or enhanced transceivers are required. The specification calls for enhanced bus transceivers with controlled rise and fall times, tightly defined thresholds, low part to part skew, and low-voltage transistor-transistor logic (LVTTL) levels. During the development of this standard, specific transceivers were developed to meet these requirements.

As a source-synchronous protocol, the performance of 2eSST is determined not by the propagation delay from source to destination, but by skew – the variation in propagation delay through the drivers, backplane, and receivers. As the skew decreases, system bandwidth can increase. In theory, a source-synchronous protocol is virtually unlimited in its potential transfer rate. This standard provides for transfer rates of 160, 267, and 320 MBps with a 21-slot backplane. New transfer rates can be defined as the technology improves.

In developing the 2eSST protocol, several important objectives were considered:

- Maximize performance: Performance was the driving impetus for this new protocol. To meet this objective, the protocol was designed to ensure that all devices involved in the transfer would operate as fast as possible.

- Minimize complexity: The 2eSST protocol was designed to minimize the amount of logic that would be required to implement the protocol.

- Minimize application limits: The 2eSST protocol can be used in 3U, 6U, and 9U environments.

- Maintain compatibility: The 2eSST protocol was designed to be compatible with legacy VMEbus products.

Key Contributions

- 2003: 2eSST (ANSI/VITA 1.5) – Defines VME protocol that allows data transfers up to 320 MBps.